- You are here:

- AM.CO.ZABuythisCNC Utilities Homepage

- EasyRoute-CNC-Router

- Component Manuals

- KR Inverter ACD320 Series Manual.pdf

- Page 142 of 160

ACD320 user manual

Appendix

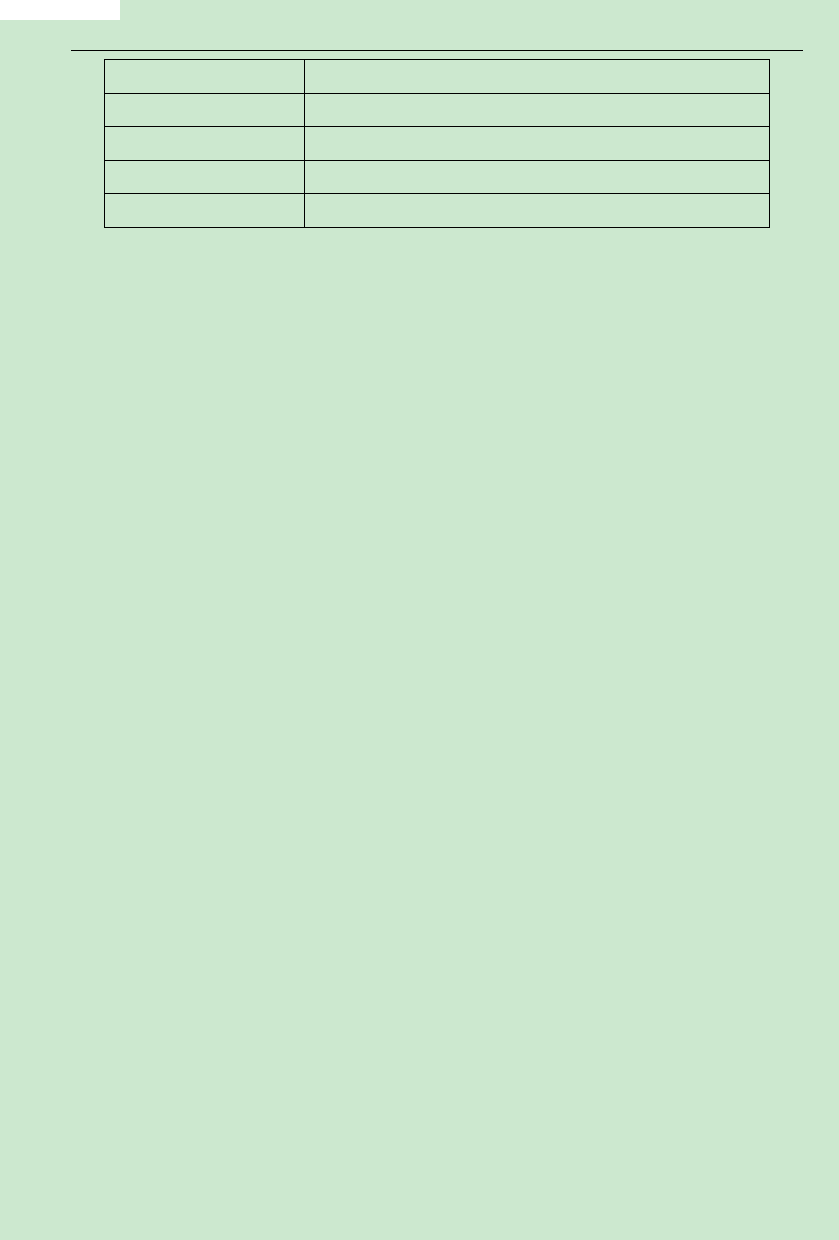

‘8’

LRC CHK Hi

‘5’

LRC CHK Lo

‘6’

END Lo

CR

END Hi

LF

6.3 Communication frame error check

Frame error check includes twoparts: byte bit check (odd/even parity check) and entire

frame data check (CRC check).

6.3.1 Byte bit check:

The user can select different bit check modes according to the actual needs. Alternatively,

the user can select "no parity". This will affect the check bit setting of each byte.

Even check: Insert a even check bit before data transmission to demonstrate the number of

"1" in data content is odd or even. If the number is even, check bit is set "0",otherwise the check

bit isset "1", so the parity remain unchanged.

Odd check: Insert a odd check bit before data transmission to demonstrate the number of

"1" in data content is odd or even. If the number is odd, check bit is set "0",otherwise the check

bit is set "1", so the parity remain unchanged.

For example, If we want to transmit "11001110", the number of "1" is 5, check bit is

"1"when use even check; check bit is "0" when use odd check. The receiver need to do the parity

checking. If the parity of received data is not the same as the preset value,the communication has

some errors.

6.3.2 Cyclical Redundancy Check (CRC):

The RTU frame format is used. The frame includes frame error detection field calculated

on the basis of CRC. The CRC field detects the content of the entire frame.The CRC field has

two bytes, including 16 bits of binary values. It is added to the frame after calculation of the

transmission device. The receiving device recalculates the CRC of the frame, and compares it

with the value in the received CRC field. If the two CRC values are not the same, it indicates a

transmission error.

CRC is first stored in 0xFFFF, and then a process is called to process over six consecutive

bytes in the frame and the value in the current register. Only the 8-bit data in each character is

valid for CRC. The start bit, stop bit and parity check bit are invalid.

During CRC generation, each 8-bit character independentlyconducts (XOR) with the

content of the register, the result moves to the least significant bit (LSB) direction,and the most

significant bit (MSB)is filled in with 0. LSB is extracted for detection. If LSB is 1, the register

- 137-